Altimime表示,他们之前研究过这些材料,目前这些材料展现出非常精确的层状架构设计,最佳化了DC/AC电气性能,并具备良好的R-off到R-on比。I

基于金属氧化物的非挥发性存储器 ──电阻式RAM(RRAM),在11nm节点前不可能进入市场;在此之前,堆叠式浮闸NAND闪存相对较具潜力,而且很可能会朝向2~4Tbit的独立型整合芯片发展,IMEC研究所存储器研究专案总监Laith Altimime说。

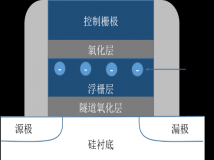

Altimime揭示了闪存发展蓝图,并展示在17nm节点采用垂直8层堆叠,从传统浮闸闪存转换到所谓的SONOS闪存。他声称在14nm~11nm节点堆叠数量还可增加到16层。而RRAM要进入实际应用,也必须拥有类似的堆叠架构才能在市场上竞争。SONOS全名为Silicon Oxide Nitride Oxide Silicon(硅-氧-氮化硅-氧-硅)。

IMEC已经和主要的存储器制造商,包括尔必达(Elpida)、海力士(Hynix)、美光科技(Micro)和三星(Samsung)等,就闪存和后续的存储器技术展开合作。但这份名单中显然缺少了东芝(Toshiba)。目前所提出的存储器晶体管堆叠均为独立芯片(monolithic),但未来除了芯片堆叠外,也可能会在封装阶段进行。

IMEC表示,RRAM必须注意11nm节点后与闪存发展蓝图的交会点

针对RRAM,IMEC主要瞄准基于铪/氧化铪的材料。Altimime表示,他们之前研究过这些材料,目前这些材料展现出非常精确的层状架构设计,最佳化了DC/AC电气性能,并具备良好的R-off到R-on比。IMEC也认为它具有良好的开关机制,这与晶格中的氧空穴(oxygen vacancies)运动有关。

在今年六月的VLSI技术研讨会中,来自IMEC的研究团队就SiO2/HfSiO/NiSi材料分析了RRAM的热丝性能(filament properties),展示如何依照可藉由量子力学传导模型而量化的热丝性质在高电阻状态实现最小电流。

在华盛顿的国际电子设备会议(International Electron Devices Meeting)中,IMEC的研究人员也提出了基于HfO2的RRAM单元,其尺寸小于10nmx10nm,具有HF/HfOx电阻元件(resistive element),每位元开关能量约0.1pJ或更低。其耐受性为5x10^7周期。然而,IMEC还未进行大规模阵列或RRAM的堆叠设计。“我们主要是为合作伙伴展示概念。每家公司都会有自己的芯片设计,”Altimime说。

走向堆叠

RRAM的高读写周期数,是该技术超越闪存的关键优势──闪存的耐受周期正随着芯片微缩而减少。在22nm节点,闪存的耐受周期大约低于10^4。

这也是存储器厂商竞相寻求下一代最新存储器技术的主要原因,惠普最近和Hynix宣布2013年底前将推出商用化的忆阻器存储产品(参阅电子工程专辑报道:“闪存终结者”忆阻器或于2013年商用化)。

然而,Altimime表示,他对此感到相当惊讶。“你将浮闸推展到极限就意味着3D了。针对16nm浮闸,3D BiCS是可用的,”他指的是东芝所提出的3D NAND闪存选项。

大多数存储器制造商都提出了3D闪存架构,如东芝和SanDisk的P-BiCS(pipe-shaped bit cost scalable);三星的TCAT(terabit cell array transistor);VSAT(vertical stacked array transistor)和VG(vertical gate)等。

通过整合单芯片的8、16或32层等非挥发性存储器元件,平面设计规则可以放宽或至少维持在目前的25nm左右,但尺寸仍然超越2D存储器。事实上,Altimime表示,为达到可接受的良率,平面设计规则必须再放宽。层数愈多,代表设计愈复杂,且良率更低。因此,其开发重点会集中在将各种技术折衷并最佳化,包括关键尺寸、独立芯片整合以及多芯片整合,Altimime说。

“从研发到实际商品化还需要3~4年的时间。我们制订了工程时间表,我们认为堆叠式闪存将会优先,而后可能会是RRAM。”

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。