与现在的7nm工艺相比,3nm工艺可将核心面积减少45%,功耗降低50%,性能提升35%。

尽管日本严格管制半导体材料多少都会影响三星的芯片、面板研发、生产,但是上周三星依然在日本举行了“三星晶圆代工论坛”SFF会议,公布了旗下新一代工艺的进展,其中3nm工艺明年就完成开发了。

三星在10nm、7nm及5nm节点的进度都会比台积电要晚一些,导致台积电几乎包揽了目前的7nm芯片订单,三星只抢到IBM、NVIDIA及高通部分订单。不过三星已经把目标放在了未来的3nm工艺上,预计2021年量产。

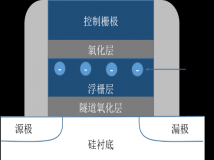

在3nm节点,三星将从FinFET晶体管转向GAA环绕栅极晶体管工艺,其中3nm工艺使用的是第一代GAA晶体管,官方称之为3GAE工艺。

根据官方所说,基于全新的GAA晶体管结构,三星通过使用纳米片设备制造出了MBCFET(Multi-Bridge-Channel FET,多桥-通道场效应管),该技术可以显著增强晶体管性能,主要取代FinFET晶体管技术。

此外,MBCFET技术还能兼容现有的FinFET制造工艺的技术及设备,从而加速工艺开发及生产。

在这次的日本SFF会议上,三星还公布了3nm工艺的具体指标,与现在的7nm工艺相比,3nm工艺可将核心面积减少45%,功耗降低50%,性能提升35%。

在工艺进度上,三星今年4月份已经在韩国华城的S3 Line工厂生产7nm芯片,今年内完成4nm工艺开发,2020年完成3nm工艺开发。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。