台积电从原来的晶圆制造代工角色,逐步跨界至封测代工领域(InFO、CoWoS及SoIC等封装技术),试图完整实体半导体的制作流程。

半导体联盟消息,台积电从原来的晶圆制造代工角色,逐步跨界至封测代工领域(InFO、CoWoS及SoIC等封装技术),试图完整实体半导体的制作流程。

根据不同产品类别,台积电的封测技术发展也将随之进行调整,如同HPC(High Performance Computer)高效能运算电脑将以InFO-oS进行封装,服务器及存储器部分选用InFO-MS为主要封装技术,而5G通讯封装方面即由InFO-AiP技术为主流。

透过上述不同封装能力,台积电除本身高品质的晶圆制造代工能力外,更藉由多元的后段制程技术,满足不同客户的产品应用需求。

台积电积极发展封测技术如InFO-AiP,有效缩减元件体积并强化产品功能

面对AI、5G通讯时代逐步来临,台积电作为晶圆制造的龙头大厂,除了钻研更精密的线宽微缩技术外(由现行7纳米制程,逐步演进至5纳米,甚至3纳米制程条件),封测代工领域也是另一项发展重点指标。透过前述相关封测技术(如InFO-oS、InFO-MS及InFO-AiP等)的开发,台积电试图整合元件制造与封装能力,藉此提供客户较完整的实体半导体之制作流程及服务,以满足各类高端产品轻、薄、短、小的使用目标。

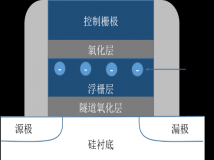

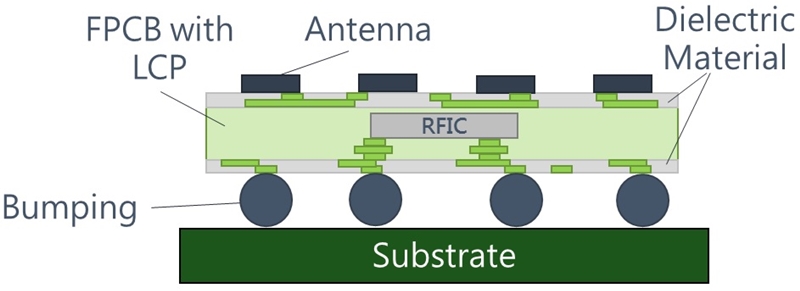

值得一提,台积电在5G通讯领域中主打的InFO-AiP(Integrated Fan-out Antenna in Package)封装技术,于后续即将开展的毫米波(mm-Wave)通讯时程,也将扮演极重要角色。如同前述,结合台积电本身先进半导体制造能力,使线宽精细度得以提高外,再搭配自身研发的独门封装技术InFO-AiP,将驱使整体元件体积有效缩减10%,并且强化天线讯号增益四成成效。

▲台积电之InFO-AiP结构示意图。(Source:拓墣产业研究院整理,2020.2)

不同于封测代工厂商,台积电发展策略仍以晶圆制造为主、封测代工为辅

考量台积电对5G毫米波AiP封装技术之积极抢市态度,对现行封测代工厂(如日月光、Amkor、江苏长电及矽品等)而言,发展策略已产生不小的竞争压力。假若设想于技术研发为企业发展及策略重点时,则台积电于封装策略的开发进程,将有别于其他封测代工厂商的政策目标。

由于台积电的主力强项为高精密晶圆制造代工,将能提供客户复杂且整合度较高的半导体制造服务,藉此因应如AI及通讯元件等高阶产品的市场需求;然而只专精于半导体晶圆制造代工,对龙头厂商的发展性而言似乎略显不足。依现行发展脉络,台积电除了高端晶圆制造外,更进一步搭配自身开发的封装技术,以延续元件制造中线宽微缩的目标趋势,使封装中的重分布层(RDL)金属线路,能透过较精细的制作方式,进行后段的堆叠程序,最终达到有效降低元件体积,并提高产品的功能性。

台积电对半导体的发展策略,仍以晶圆制造为主、封测代工为辅,目前将重心摆在自身高端晶圆制造代工能力,搭配相关先进封测技术开发,期望完整实体半导体的制作流程。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。