来自cnBeta的消息,三星在SFF论坛上公布未来四代芯片工艺演进路线图。

近年来,摩尔定律似乎变得有些不大灵验。但从另一视角来看,该定律并没有就此告别舞台。在本周二于硅谷举办的 SFF 论坛上,三星宣布了该公司的新芯片制造计划,披露了未来几代产品的发展方向。芯片制程的一个关键部分,就是缩小晶体管的大小。这种非常微小的电子开关,可以在特定时钟频率下处理我们拥有的各种数据,涵盖从微波炉、到手机上的人工智能等在内的各种算法。

不过随着芯片组件的规模越来越接近单个原子,其变得越来越难以跟上摩尔定律的步伐。几十年来,它曾很好地预示了“每隔两年,同等大小的芯片里的晶体管数量可以增加一倍”。

Moor Insights and Strategy 分析师 Patrick Moorhead 表示,摩尔定律并未消逝,只是有所放缓,芯片行业不得不更加努力提升其性能,比如专用的 AI 或图形处理器,以及用更好的方法将多个芯片打包到一起。

好消息是,在今年的 SFF 论坛上,三星分享了该公司发展“极紫外光刻技术”的长期承诺。这条通往新工艺的道路,有望将芯片上的电子电路数量增至四倍。

路线图显示,三星规划了四代处理器的工艺目标:

● 今年,三星将将开始部署基于极紫外光刻技术的 7nm 芯片制造工艺;

● 接着,该公司有望将电子元件收缩到 5nm 的制程,同时降低其功耗;

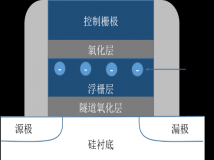

● 然后,将制程进一步缩到 4nm,这也是 FinFET 晶体管工艺的绝唱;

● 最后,是基于‘栅全包围’(GAA)的 3nm 制程技术。

每一步的发展,都将使晶体管变得更加复杂,并推升了制造成本。至于单个晶体管成本在未来路线图中会发生什么样的变化,三星没有立即置评。

声明: 此文观点不代表本站立场;转载须要保留原文链接;版权疑问请联系我们。